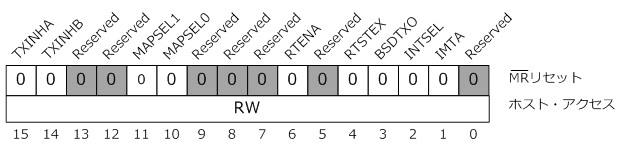

マスター・コンフィグレーション・レジスタ1��0x0000��

こ��16BitレジスタのすべてのBitは、リード/ライト可能で、��ストによって完��に維持されます��MRマスター・リセ����後にクリアされ�� RTRESET Bitによるリセ����の影響を受けません��

| ビッ�� | 名称 | R/W | 初期値 | 説�� | |||

| 15 | TXINHA | R/W | 0 |

バスA送信禁止 こ��ビット��、「TXINHA」��力ピンと論理和を取ります。このレジスタ・ビットと対応するTXINHAピンはRTに全体的に影響します�� こ��禁止は、バスAのすべての送信を無効にします�� |

|||

| 14 | TXINHB | R/W | 0 |

バスB送信禁止 こ��ビット��、「TXINHB」��力ピンと論理和を取ります。このレジスタ・ビットと対応するTXINHBピンはRTに全体的に影響します�� こ��禁止は、バスBのすべての送信を無効にします�� |

|||

| 13-12 | Reserved | 未使用、読み出し時常�� 00 | |||||

| 11-10 | MAPSEL1:0 | R/W | 0 |

マップ��アドレス・ポインタ��MAP����選�� ホス��SPIは、多くのSPIレジスタまた��RAMアクセスのハ��ドウェアメモリアドレスポインタに依存して����す�� こ��2ビット��フィールド��、SPIトランザクションに対してどのMAPがアク����ブであるかを示します�� |

|||

| Bit 11-10 |

アク������ マッ�� |

MAPレジスタ アドレス |

有効SPI opコー�� |

||||

| 0-0 | MAP1 | 0x000B | 0xD8 | ||||

| 0-1 | MAP2 | 0x000C | 0xD9 | ||||

| 1-0 | MAP3 | 0x000D | 0xDA | ||||

| 1-1 | MAP4 | 0x000E | 0xDB | ||||

| 9-7 | Reserved | 未使用、読み出し時常�� 00 | |||||

| 6 | RTENA | R/W | 0 |

RT有効 こ��ビットが0のとき、RT動作��無効になります�� こ��ビットが1のとき、RTは有効ですが、動作��RTSTEXレジスタ・ビット��状態によって制御されます�� |

|||

| 5 | Reserved | 未使用、読み出し時常�� 0 | |||||

| 4 | RTSTEX | R/W | 0 |

RT実行開�� レジスタBit6��1のとき、このビットをセ����するとRTの動作が開始されます�� 一旦実行後��、このビットをリセ������また��RTENAレジスタビット)すると、すぐにRT動作が停止します�� |

|||

| 3 | BSDTXO | R/W | 0 |

バス・シャ����ダウン送信のみ こ��ビット��、RTが有効な場合にのみ適用されます�� (a) RTINHAビットまた��RTINHBビットが「Remote Terminal Configuration Register (0x0017)」に設定されて����。また�� (b) RTが、MC4また��MC21の有効な「バス・シャ����ダウン」モード��コード��コマンドを受信したときに��1553バス禁止の動作を決定しま�� |

|||

| 2 | INTSEL | R/W | 0 |

IRQ出力タイプ��選�� こ��ビットが0のとき、有効にされた割り込みイベントが発生すると、IRQ��割り込み要求)��力��1μsの��パルスを生成します�� こ��ビットが1のとき、IRQ出力��IRQをHigh状態にするためのホスト動作を����とする連続的なLowレベル出力で構��されます�� レベル割り込みが有効にされると、��スト��ACKIRQ入力ピンを少なくと��250nsアサートしてIRQをネゲートします�� |

|||

| 1 | Reserved | 未使用、読み出し時常�� 0 | |||||

| 0 | Reserved | 未使用、読み出し時常�� 0 | |||||